| T O P I C R E V I E W |

| Bjäris |

Posted - 2015/04/24 : 12:30:14

Hej

Jag har börjat fundera lite på att bygga ett digitalt delningsfilter med digitala ingångar och analoga utgångar.

Jag har tidigare byggt med DAC chipet PCM1792, och PGA2320 för volymkontrollen, men det är ett antal år sedan. Är det fortfarande ett bra val, eller har utvecklingen gått framåt.

http://www.hififorum.nu/forum/topic.asp?TOPIC_ID=85240

|

| 25 L A T E S T R E P L I E S (Newest First) |

| soundbrigade |

Posted - 2018/12/16 : 12:51:46

Alla fraktbolag är skyldiga att klarera gods. Tycker nog DHL, även om bolaget fått lite skit, är mer tillförlitligt än PostNord. Dessutom har jag fått kort, helt nyligen, levererat av DHL och har fått en faktura i efterhand. Snabb och säker frakt och inget jiddrande med Postens besynnerliga och något slumpvisa behandling. |

| Bjäris |

Posted - 2018/12/16 : 12:31:34

Nu har jag läst på lite på DHLs hemsida. Ser ur som att det blir 85 kr i moms och 62,50 i extra avgift till DHL. |

| Bjäris |

Posted - 2018/12/16 : 12:20:41

Jag vet inte, men det visar sig snart, för paketet är på väg.

Jag tittade på vad jag betalade när jag beställde vis UPS, och då var det momsen + 19 kr. Det är i alla fall betydligt lägre än postens 75 kr. |

| Lovan |

Posted - 2018/12/14 : 20:15:10

DHL har väl en motsvarande avgift? |

| Bjäris |

Posted - 2018/12/05 : 21:57:45

Hej, är det någon av er som har erfarenhet av hur det är att skicka efter paket från kina efter postnords extra avgift? Jag är nästan klar med mönsterkorten till nästa version av filtret. Så nu är frågan om man bör välja posten eller lägga till lite och skicka med DHL. |

| Bjäris |

Posted - 2018/04/21 : 22:42:35

Nu har jag har testat att få till längre FIR filter än 1536 tappar, men har stött på problem med att logiken i fpga:n tar slut. Egentligen så är det ramminnet (bram) i fpga:n som tar slut, och då försöker programmet använda logik som ramminne, vilket gör att logiken tar slut väldigt fort. Eftersom jag använder den största fpga:n från xilinx som jag har hittat (XC6SLX9) som inte har BGA kapsel, så blir det omständigt att byta till en större. Tills vidare får det duga med filtren som jag redan har. Sen har jag lite andra funderingar, med det får bli ett kommande problem.

Ett annat problem som jag har är att när jag byter förstärkare till en med högre känslighet, så blir det vitt brus i högtalarna som är precis hörbart på lyssningspositionen. Jag satte dit analoga volymkontroller på utgångarna, för att slippa den här problematiken, men tydligen är PGA2320 inte tillräckligt lågbrusiga. Det gör ingen skillnad om jag höjer eller sänker volymen, så bruset verkar komma från volymkontrollkretsarna. Planen just nu är att sätt en spänningsdelare i kablaget till effektförstärkaren som dämpar 20dB. Det borde sänka bruset så att det inte blir hörbart, och jag kommer fortfarande kunna bottna effektförstärkaren med god marginal. |

| Bjäris |

Posted - 2018/03/04 : 12:47:59

Just nu planerar jag inte att ändra mera på IIR filtret, därför får det bli ett eget inlägg

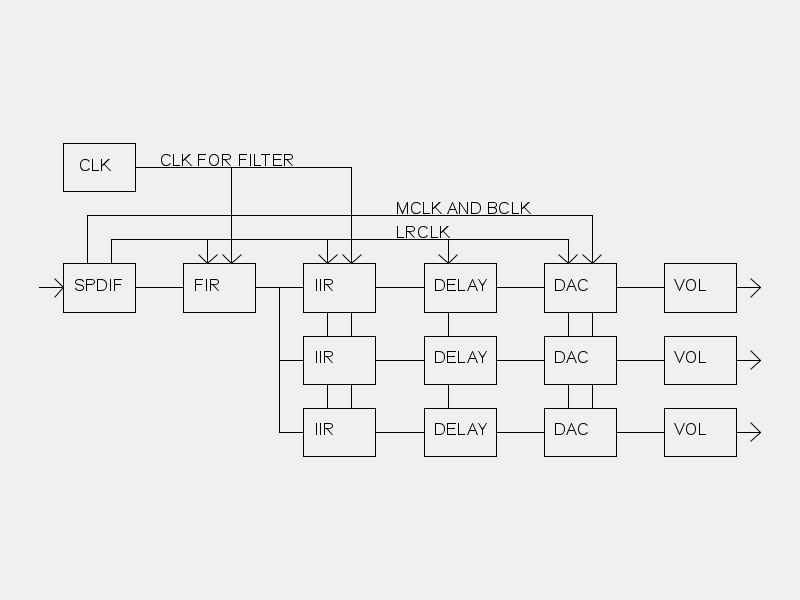

IIR filtret är tänkt att användas som delningsfilter. Systemet har tre stereo utgångar, som kan användas t.ex. för bas, mellan och diskanthögtalare.

Nedan finns ett förenklat blockschema för att visa vad jag gör med ljudsignalen på kretskortet.

Filtren är uppbygda i biquad moduler. Kanal ett och tre har två stycken, och kanal två har fyra st.

Varje biquad behöver 5st 35 bitars konstanter. För varje samplingsfrekvens behövs en egen uppsättning konstanter. Detta leder till att det totalt behövs: 6 st fs * 8 st biquad * 5 konstanter/biquad = 240 st 35 bitarskonstanter. Eftersom det hade varit lite omständigt att skriva om dessa för hand varje gång man vill ändra delningsfrekvens har jag skrivit ett scilabskript som skapar vhdl filen med konstanterna i.

I filen finns även presets för amplitud och tidsfördröjning till de olika utgångarna. Om man i stället vill att värdet som sätts i menyn ska sparas till nästa gång som filtret startas upp, kan delayerna sättas till 255 och amplituderna till + 10,5 dB. Då laddas värdena från eeprom kretsen i stället.

http://privat.bahnhof.se/wb468040/DigitalFilter1/IIRFilter/makeIIRROM.sce |

| Bjäris |

Posted - 2018/03/03 : 15:30:24

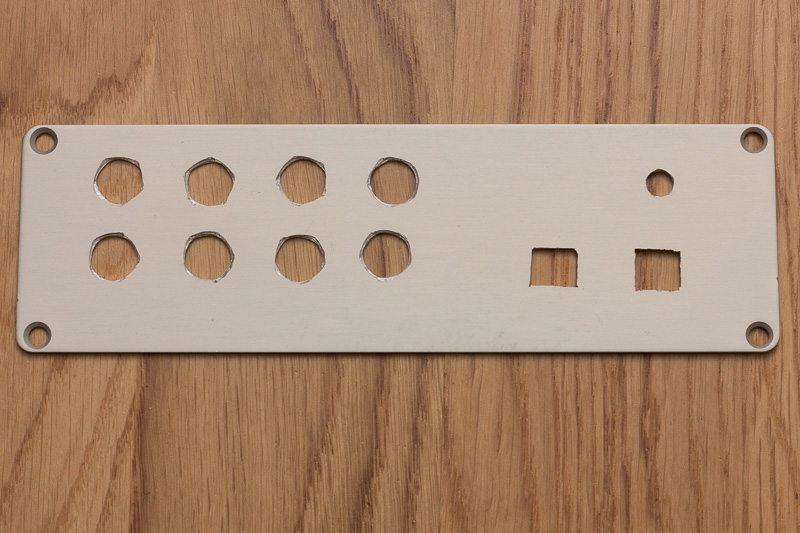

Nu har jag även fått till en front.

Jag har bytt ut aluminiumfronten som följde med lådan mot en plexiglasskiva. Sen när jag börjar bli klar ska jag ta bort skyddsplasten och maskera baksidan med en svart pappskiva, så att endast displayen och IR Senson syns.

Sen har jag börjat med en hemsida för att kunna ladda upp bilderna till forumet, och dokumentera mina små projekt. Hoppas att någon kan ha någon nytta av den någon gång i framtiden.

http://privat.bahnhof.se/wb468040/index.html |

| Bjäris |

Posted - 2018/02/21 : 22:38:06

Jag hade för mig att man inte fick tillgång till microblaze processorn om man kör ISE Design Suite: WebPACK Edition, men det kanske de har ändrat, för det ser ut som att den följer med nu när jag tittar på deras sida.

HLS modulen kanske jag borde titta mer på. Nästa steg kommer nog bli att göra ett litet omtag på FIR filtret. Som det är nu använder jag 4 st dsp kärnor per multiplikation för att klara 24 bitars data. Men om jag bara använder 18 bitarskonstanter och multiplicerar de sista 6 bitarna i datat för sig, utanför dsp kärnan, så borde det räcka med en dsp kärna per multiplikation. När jag har studerat det vidare så ser 18 bitarskonstanter ut att vara mer än tillräckligt. |

| HerrD |

Posted - 2018/02/21 : 20:11:05

Assembler, du gör det inte enkelt för dig... Hatten av! Jag hade hade valt en latare väg med MicroBlaze och C och skrivit fir-filtren i hls för enklare optimering. Kul att det meckas på riktigt i alla fall  |

| Bjäris |

Posted - 2018/02/21 : 19:13:51

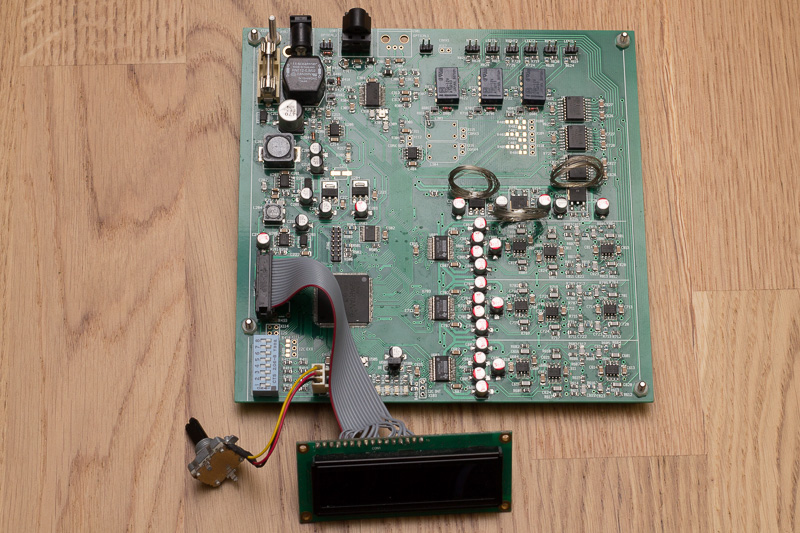

Det var ett tag sedan jag skrev något i den här tråden, men arbetet har inte stått stilla.

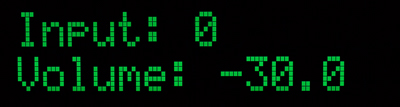

Eftersom menysystemet har fått det jag tror är dess slutliga form, så lägger jag upp det som ett inlägg.

För att hantera menysystemet, I2C kommunikation, och inställningarna för resten av logiken i FPGA:n används en picoblaze soft processor core från Xilinx. Denna programmeras i sin tur i assembler.

I den här menyn kan pilarna upp/ned användas för att ställa in volymen, och höger/vänster för att välja ingång. Play/Pause kan användas för att muta ljudet, och Menyknappen för att välja Meny 1.

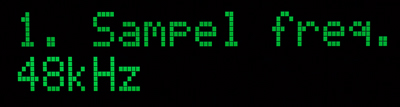

Den här menyn används för att visa vilken samplingsfrekvens källan levererar. Pilen till höger går till nästa meny, och menyknappen används för att återgå till Main Menu.

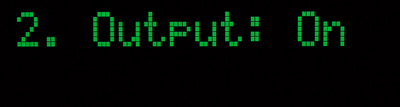

Den här menyn används för att aktivera, pil upp, eller avaktivera utgånen, pil ned. Pilen till höger/vänster går till nästa eller föregående meny, och menyknappen används för att återgå till Main Menu.

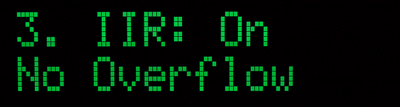

Den här menyn används för att aktivera, pil upp, eller avaktivera IIR filtret, pil ned. IIR filtret används som delningsfilter. Den nedersta raden indikerar om det finns overflow i filtret, så att filterkonstanterna behöver justeras. Pilen till höger/vänster går till nästa eller föregående meny, och menyknappen används för att återgå till Main Menu.

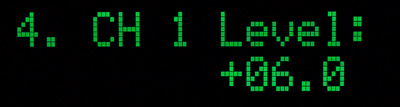

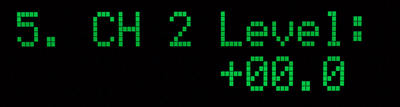

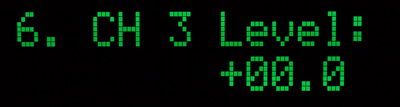

De här menyerna används för att ställa nivån på respektive utkanal, pil upp, för att öka nivån, och pil ned, för att minska nivån. Nivån kan ställas med +/-10 dB. Pilen till höger/vänster går till nästa eller föregående meny, och menyknappen används för att återgå till Main Menu.

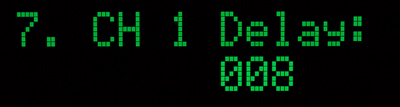

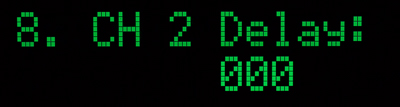

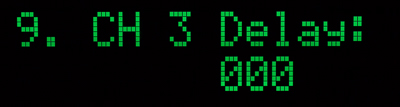

De här menyerna används för att ställa fördröjning på respektive utkanal, pil upp, för att öka fördröjningen, och pil ned, för att minska fördröjningen. Fördröjningarna kan ställas mellan 0 och 5,67 ms. Varje steg ger 22,7 us fördröjning vilket motsvarar 7,7 mm. Pilen till höger/vänster går till nästa eller föregående meny, och menyknappen används för att återgå till Main Menu.

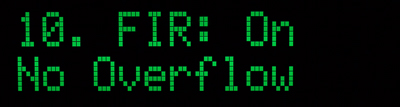

Den här menyn används för att aktivera, pil upp, eller avaktivera FIR filtret, pil ned. FIR filtret används för att korrigera nivåerna och fasläge från högtalaren, och rummet. Den nedersta raden indikerar om det finns overflow i filtret, så att filterkonstanterna behöver justeras. Pilen till höger/vänster går till nästa eller föregående meny, och menyknappen används för att återgå till Main Menu.

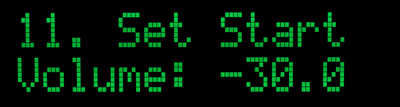

Den här menyn används för att ställa volymen vid uppstart. Pil upp, för att öka nivån, och pil ned, för att minska nivån. När nivån ställs ändras även volymen till den stälda nivån. Pilen till höger/vänster går till nästa eller föregående meny, och menyknappen används för att återgå till Main Menu.

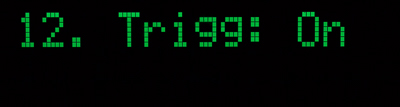

Den här menyn används för att aktivera, pil upp, eller avaktivera 12V trigg, pil ned. Pilen till vänster går till föregående meny, och menyknappen används för att återgå till Main Menu.

Det här inlägget blev lite stelt och styltigt, men jag hoppas att det ger en bild av vad jag gjort på projektet den senaste tiden och att det kan ara till någon glädje. |

| Bjäris |

Posted - 2017/05/25 : 21:39:54

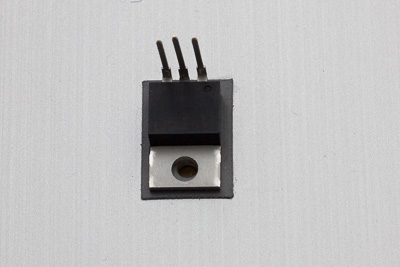

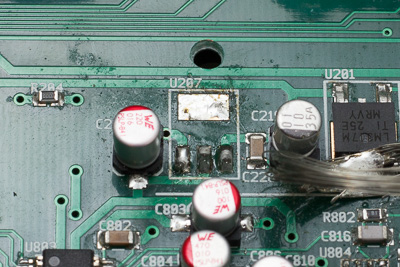

Eftersom spänningsregulatorn som tar ned 12 V till 5 V åt DA-omvandlarnas analog del blir för varm för min smak, så har jag bytt kylningsfilosofi på denna. Jag vet inte om den blev så varm att det var skadligt, men den var lite för varm för att jag skulle kunna hålla kvar handen på den. Tidigare använde jag en avskalad ledare med många utspridda kardeler för att öka avkylningsytan, men jag känner mig lite osäker hur effektivt det är nu när det kommer på ett lock och luften under kommer att stå still. Därför har jag borrat hål i kretskortet och sätter en TO220 kapsel med skruv ned i bottenplattan för att leda bort värmen. Det är en teknik som tidigare har visat sig fungera väldigt bra, och jag kan i det här fallet inte känna någon förhöjd temperatur under kretsen.

Det stora hålet används för att sticka ned en skruvmejsel och dra åt skruven som håller TO220 kapseln mot lådans botten.

|

| Bjäris |

Posted - 2017/05/25 : 15:16:45

Nu kommer nog den här tråden övergå från att vara en diskusionstråd till ett bildreportage/byggtråd. Jag hoppas att ni inte har något imot det, trotts att den kommer bli lite felplacerad. |

| Bjäris |

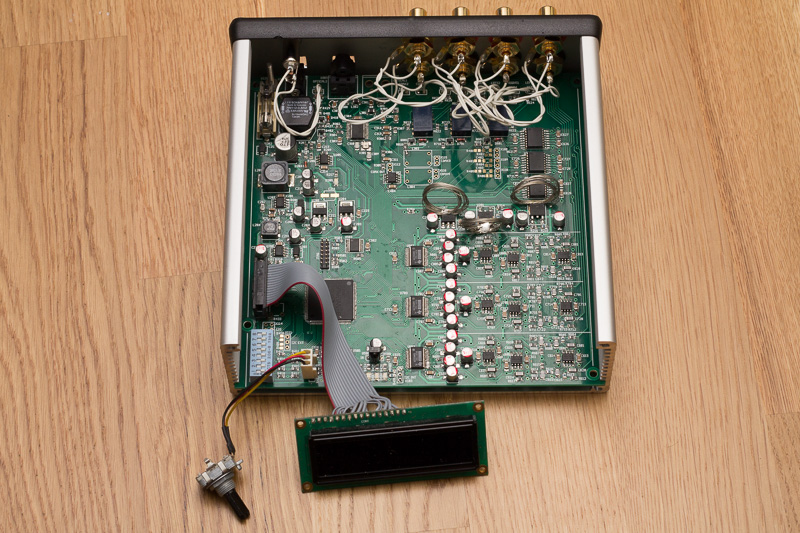

Posted - 2017/05/24 : 22:01:02

Sedans förra inlägget har jag optimerat lite mer och använder 12 av 16 DSP kärnor till fir filtret och får till 1536 tappar. En dsp kärna används till IIR filtren för att dela upp till de tre registren med 24 dB/oktav.

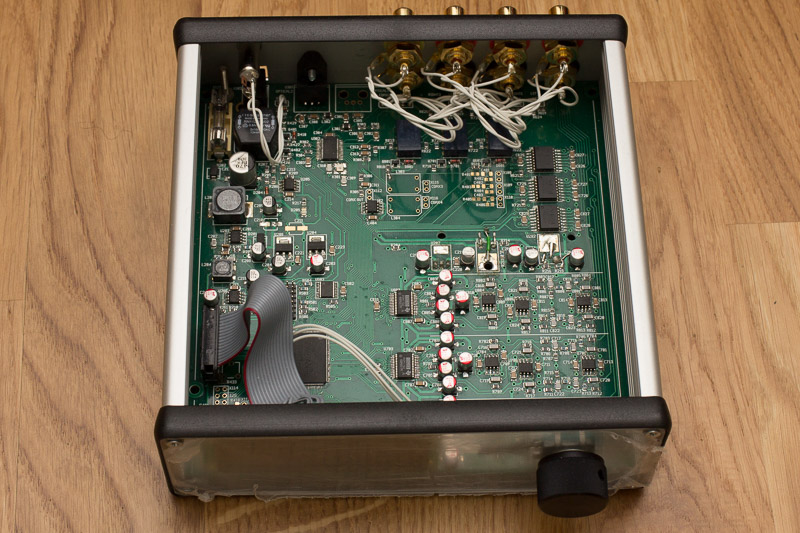

Nu är arbetet i full gång för att bygga in kretskortet i en låda.

|

| Bjäris |

Posted - 2017/02/12 : 19:46:46

Lite snabb optimering, gav mig 512 tappars FIR filter, så nu är det dags att mäta upp mina testhögtalare. Tror ni följande utrustning kan vara användbar? Själv är jag lite tveksam till linjäriteten i mixerbordet..

https://www.dropbox.com/s/csqz922c59ufe38/M%C3%A4tinstrument.jpg?dl=0

Jag fick inte till inbäddningen av bilden, så ni får klicka på länken. |

| Bjäris |

Posted - 2017/02/11 : 15:28:41

Hej!

Nu tänkte jag rapportera nästa stora steg framåt!

IIR filter för delningen fungerar, och jag har fått i gång FIR filtret för att kompensera för frekvensgång och fas fel i högtalarna.

Så nu kan jag skapa filter i rePhase som jag sedan kan använda i min design. Fir filtret klarar just nu 256 taps, men förhoppningsvis är jag efter lite optimering snart uppe i 1536. |

| Bjäris |

Posted - 2016/10/31 : 22:38:55

Nu har jag felsökt sedans i semestern i somras och försökt förstå vad som inte fungerar på IIR filtret som jag har tänkt använda som delningsfilter. Allt fungerade jättebra när jag simulerade på behavioral nivå, men sen går allt åt skogen när jag kör koden i FPGA eller simulerade på post-translate nivå. Så efter väldigt mycket felsökning, angrep jag problemet från ett annat håll och fick dubbelt så mycket kod, som inte är lika snygg, men det funkade efter en halv dags arbete, så nu är jag på banan igen! Så gött!

Nu ska jag försöka få till lite menyer, så att man kan ställa in volymen och tidsfördröjning på de olika elementen. Där efter hade jag tänkt mig ett stort fir filter som ska korrigera återstående olinjäriteter. Sen ska jag börja bygga mina drömhögtalare. Frågan är om det kommer ta mer eller mindre än 10 år..

|

| Bjäris |

Posted - 2016/05/01 : 11:41:05

Enligt vad jag har läst, så beror hoppen på att det inte finns någon oscillator som har en jämn multipel av 44100 på raspberry pi. Därför ser signalen ut som den gör. Lite intressant läsning finns på länken nedan.

https://www.raspberrypi.org/forums/viewtopic.php?t=8496 |

| iMac |

Posted - 2016/04/29 : 14:57:26

Stämmer, mätningen är gjord direkt på I2S linan på raspberryn. Kan vara avbrott eller någon klockfrekvens som varierar beroende på CPU belastning som gör att den hoppar.

Skulle vara intressan att göra samma mätning med en Beaglebone, fast mata den med en extern master clock! |

| Bjäris |

Posted - 2016/04/28 : 22:32:12

Anledningen till att bitklockan ser ut som det gör beror väl på att oscillatorn i raspberry pi inte har en lämplig oscillator att utgå ifrån, så den hoppar lite mellan frekvenserna som du mätt upp. Jag antar att du har mätt bitklockan direkt på I2S signalen från raspberry pi?

Frågan är hur mycket av detta som finns kvar efter att signalen har passerat hifiberry med en WM8804 och in gången på mitt kort som består av en WM8805. Sen är det ytterligare en fråga hur mycket jittret förstör utsignalen från DA-omvandlaren. |

| iMac |

Posted - 2016/04/28 : 01:04:26

MCLK ser inte så bra ut på min Raspberry PI Mod B, verkar vara lite splittrad mellan 2,809 o 2,825MHz..

[/URL] [/URL] |

| Bjäris |

Posted - 2016/04/24 : 11:00:39

Hej, efter lite flyttande så börjar jag komma igång igen. Jag har gjort ett fifo i FPGA:n för att testa hur stort problemet med jitter från raspberry pi är. Uppsätningen är som följer.

Alt 1. Raspberry pi 1B med volumio installerat, som spelar upp en flac fil. Där i från går ljudet via en hifiberry via spdif till mitt kretskort, genom FPGA:n orörd och sidan vidare till DA omvandlarna.

Alt 2. Samma som ovan, men i FPGA:n går ljudet in i ett fifo, väntar ca 0,25s och klockas ut med en separat klocka och vidare till DA omvandlaren.

Jag kan inte säga att jag med säkerhet hör någon skillnad på ljudet, så jag skulle nog säga att jitterproblemen med raspberry pi är överdrivna, i alla fall med den uppsättningen av DA omvandlare mm som jag har valt. Nästa steg blir att få till filter! |

| Bjäris |

Posted - 2016/01/09 : 23:44:20

Efter lite labbande under dagen, så har jag fått ut ljud från alla tre kanalerna på kretskortet! Så snart är det dags att börja ta fram filter.

Ett av problemen är att det det blev en skälvavägning i spänningsinvertern, som gjorde att jag fick en sinus på ca 15 kHz ovanpå likspänningen, men det löste sig med en kondensator i återkopplingslopen. Nu är det största problemet att de linjära spänningsregulatorerna till analogdelen blir varmare än vad jag hade tänkt mig. |

| lusse |

Posted - 2015/12/30 : 08:53:19

Jag håller med om at HD10 inte låter speciellt bra. Men för pengarna så låter det bra. Men det finns ju kort med fyra s/pdif utgångar där man kan ha olika dacar för varje register. Är det någon som har testat detta? |

| more10 |

Posted - 2015/12/19 : 17:48:30

Jag har en MiniDSP HD 4x10. Jag är inte särskilt imponerad. Jag tror att dom har för billiga op-ampar och DAC-chip. Framför allt är det digital volymkontroll och då räcker inte 24 bitar till |